|

1 引言

音响世界已进人数字化,唯有整个音响系统的心脏――功放,它长期徘徊在数字化的门外。众多知名半导体制造商都将目光聚焦在此,研制数字功放。这里简要介绍数字功放原理与结构,并给出基于TI系列音频IC的高保真数字功放的设计思路与方法。

2 数字功放原理与结构

2.1 数字功放的原理

数字功放的基本原理:使用脉冲信号PWM驱动高速功率开关,其中PWM信号的低频部分包含调制信号。该信号通过一个低通滤波器,可将调制信号重现负载(音箱)。本质上与传统模拟功放放大模拟信号的差异在于:数字功放直接对数字音频信号放大,再进行高精度D/A转换,因此效率高达85%;保真度极佳,THD+N(总谐波失真+噪声)低于0.05%。

2.2 数字功放结构

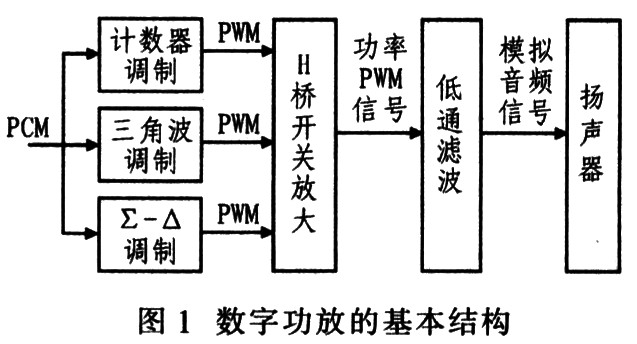

图l为数字功放基本结构,它由PWM调制器、H桥开关放大电路以及低通滤波器组成。PWM调制器将输入的数字音频信号转换成PWM信号,其中∑一△调制方法精度高,稳定性好。H桥开关放大电路则控制直流电源的通断,采用PWM信号电流向负载供电。低通滤波器能滤除开关成分,对输出波形进行平滑处理,从而得到模拟波形的音频信号。

3 TI数字音频系列IC简介

德州仪器公司(TI)长期致力于数字音频产品的研发,并取得突破性的成果。其中以TAS55xx,TAS50xx,TAS30xx,TAS-5lxx系列产品最为成熟,性价比最高。TAS55xx系列是高度集成的数字音频器,内部集成了PWM调制与DSP音效处理功能,内置8个声道,通道THD+N低于O.05%;TAS50xx系列为高精度音频PWM调制器,它只有2个声道,通道THD+N低于0.0l%,保真度极高;TAS30xx系列是专用的数字音频DSP,能实现音量、重低音调节等多种音效:而TAS51xx系列则是专用音频H桥放大电路。

4 数字音频功放设计

4.1 设计方案

这里提供2种设计方案,前者是TAS55xx+TAS51xx,可得到8通道数字功放;后者是TAS50xx+TAS30xx+TAS51xx得到2通道数字功放。因为后者设计方案保真度较高,DSP效果更好,成本更低,且所用器件在国内较易买到,以下详细介绍后一种设计方案。

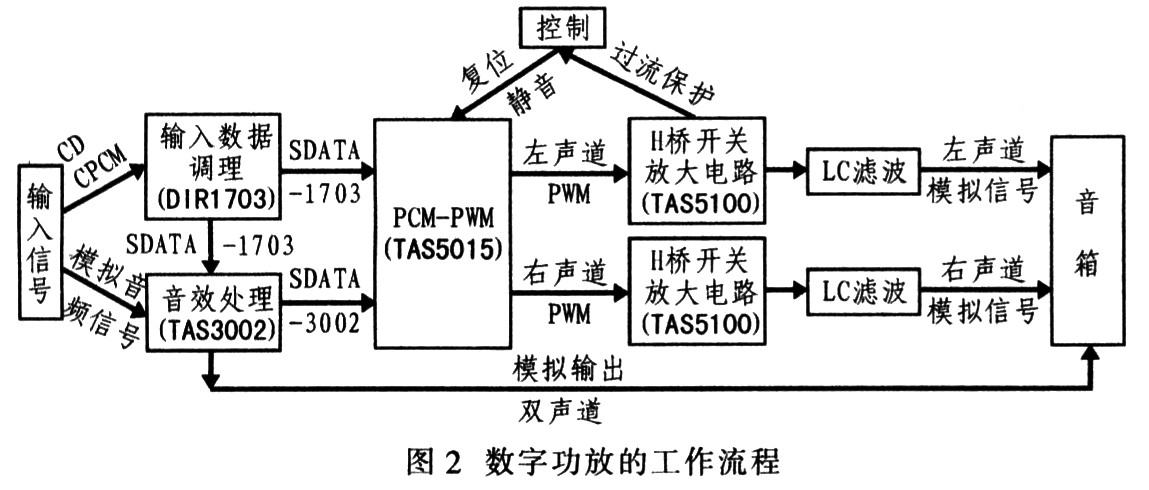

实际设计采用TAS5015+TAS3002+TAS5100的组合。其中TAS3002自带A/D和D/A转换器,使得系统可接收模拟输入信号,扩展了产品适用范围。

4.2 工作流程

图2给出数字功放的具体工作流程,音源来自两个途径:①通过高品质CD机得到的S/PDIF信号(一种被高端音响商广泛使用的数字音频格式),它通过格式转换器DIRl703转换后进入TAS3002;②模拟信号通过话筒等拾音设备被TAS3002获取。系统内数字音频信号(以SDATA表示)在TAS3002中经DSP音效处理后,进入PWM调制器TAS5015,转换成PWM信号。随后进入TAS5100进行功率放大,经低通滤波器重建模拟信号驱动扬声器。在放大过程中,如果电路出现异常,TAS5100可自动发出报警信号重置系统,也可手动重置,避免事故发生。

4.3 I2S总线

TI公司的音频器之间是以I2S(Inter―IC Sound)总线连接。I2S总线是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线音频设备之间的数据传输,广泛应用于各种多媒体系统。在I2S标准中规定了硬件接口规范和数字音频数据格式。I2S有3个主要信号:①串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2x采样频率×采样位数。②帧时钟LRCLK,用于切换左右声道的数据。LRCLK为“l”表示左声道正在传输数据,为“0”则表示右声道正在传输数据。LRCLK的频率等于采样频率。③串行数据SDATA用二进制补码表示的音频数据。有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(SysClock),是采样频率的256倍或384倍。

4.4 核心功能模块电路

4.4.1 数字音频输入

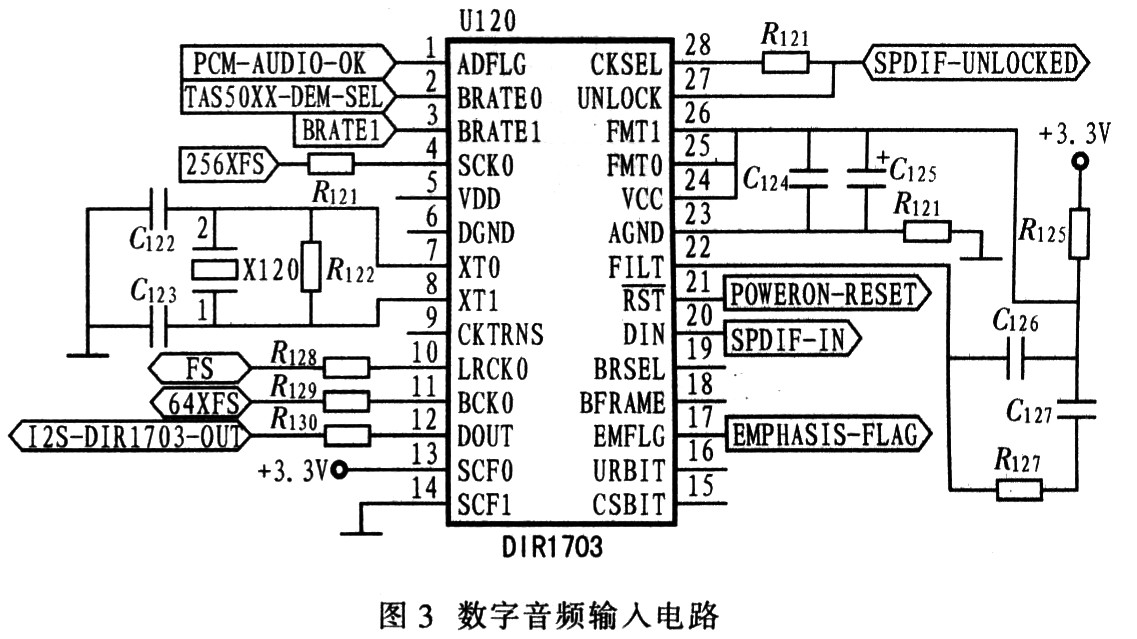

数字音频输入电路如图3所示。该模块主要利用TI的数字音频接口器件DIRl703实现以下功能:①将CD格式的数字音频信号转化为PWM调制器TAS5015可识别的串行音频数据,该数据可直接在I2S总线上传输;②产生整个I2S总线的串行时钟BCLK,帧时钟LRCLK,以及系统时钟SCLK。

DIRl703的引脚20输入的SPDIF一IN信号即为从CD唱机通过光纤或者同轴电缆得到的PCM信号;经过DIRl703处理后输出SDATA信号I2S―DIR1703一OUT;DIRl703的引脚7、8外接晶体振荡器X120,而引脚4(SCK0)输出系统时钟SCLK信号256XFS;引脚10(LRCK0)输出串行时钟BCLK信号FS;引脚11(BCK0)输出帧时钟LRCLK信号64XFS。

4.4.2 数字音频处理

数字音频处理采用了TI的数字音频处理TAS3002。PC机通过I2C接口控制TAS3002,从而得到所期望的音效。它可将模拟输入信号转化为数字信号输入或直接接收DIRl703输出的SDATA信号,并对数字输入信号进行数字式音量调节和均衡调节而无需D/A转换。然后,它可以直接将处理后的数字信号进行D/A转换为模拟信号输出以驱动扬声器发声,更重要的是它也可将处理后的数字信号直接通过I2S总线传输给PWM调制器。

如图4所示,TAS3002的引脚22接收I2S输入的SDATA信号I2S―DIRl703一OUT,或者通过引脚1和引脚40直接接收模拟信号,经TAS3002数字音效处理后,由引脚26输出处理后的SDATA信号I2S一TAS3002一OUT。同时,也在引脚7和引脚39直接给出两声道的处理后的模拟信号。

4.4.3 PWM调制

PWM调制是数字功放设计的核心。该模块采用TI公司的TAS5015PWM调制器。它接收DIRl703或TAS3002通过I2S总线传输的数字音频信号,将之转化为两声道每声道4路的PWM信号,以便下一步H桥开关放大。它能接收外部控制信号实现静音和重置,并调节采样频率。它的时钟与I2S总线同步。如图5所示,引脚17、18、19分别接收I2S总线的SCLK、LRCLK以及SDATA信号,引脚32~35输出左声道4路PWM信号,引脚26~29输出右声道4路PWM信号。

5 结语

在设计过程中最需要注意的IC间通信的同步问题,由于TI的数字音频IC都采用I2S总线通信方式,所以问题就迎刃而解。该数字功放经调试,效果极佳,性价比高。 |